# Isolated Boost DC-DC Converter with Three Switches

Minh-Khai Nguyen, *Member, IEEE*, Truong-Duy Duong, Young-Cheol Lim, *Member, IEEE*, and Yong-Jae Kim, *Member, IEEE*,

Abstract— This paper documents a new three-switch, isolated boost DC-DC converter. The major features of the proposed converter are as follows: 1) continuous input current; 2) reduced one active switch, one additional diode, and one additional capacitor; 3) unchanged primary and secondary voltage waveforms of the transformer when the duty cycle is changed; and 4) removal of the snubber circuit. This paper presents the operating principles, analysis, parameter design guidelines, and simulation results for the proposed converter. To verify the performance of the proposed converter, a 400 W prototype was constructed with a 40-60 V DC input. A PID controller was used to maintain the DC output voltage at 400 V. The simulation and experimental results matched those of the theoretical analysis.

*Index Terms*— DC-DC power conversion, current-fed full-bridge (CFFB) converter, galvanic isolation, step-up transformer, voltage double rectifier (VDR).

# I. INTRODUCTION

IGH step-up DC-DC conversion techniques are required in **M**many applications such as fuel cells (FCs), solar photovoltaic (PV) systems and uninterruptible power supplies (UPS). For these applications, a high step-up voltage ratio with high conversion efficiency is necessary. Many high step-up DC-DC converters have been proposed and investigated to convert low voltages into a constant DC bus voltage. For isolated topologies that provide galvanic isolation, voltage-fed full-bridge (VFFB) and current-fed full-bridge (CFFB) DC-DC converters are widely used [1]-[14]. Because the voltage source converters have a buck function, the major voltage gain of the VFFB DC-DC converters [1]-[4] is provided by a high-frequency transformer with a large turn ratio. To improve the voltage boost ability, a boost converter [5], [6] or an active-clamped three-level rectifier [7] is attached to the secondary side of the VFFB DC-DC converter. Because the current-fed converters have a boost function, the CFFB DC-DC converters [8]-[14] are suitable for applications with a high

1

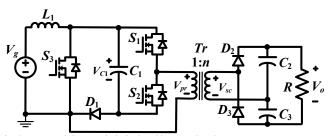

Fig. 1. Conventional current-fed, four-switch, isolated boost DC-DC converter.

step-up voltage gain. In addition, the input current ripple and turn ratio of the high-frequency transformer in CFFB converters are lower than those in VFFB DC-DC converters.

CFFB converters, however, the resonance between the leakage inductor of the transformer and the output capacitance of the primary switches causes voltage spikes in devices. To absorb the switch turn-off voltage spike in CFFB converters, a passive snubber is used [15], which causes increased power loss. To recover the energy of the snubber in CFFB converters, active clamping circuits with increasing size and cost have been proposed [16]-[19]. In an attempt to avoid the need to use the active clamping circuits, soft-switching snubberless naturally clamped CFFB converters have been proposed in [8], [9], [20] and [21].

An interleaved CFFB converter was proposed in [10] to reduce the input current ripple. By interleaving two isolated CFFB converters, the size of the magnetic components and the current stress of the devices are reduced. An input-series output-parallel connection for CFFB converter modules was proposed in [11] to increase the voltage-blocking capability at the input and decrease the current ripple at the output. A dual-input CFFB converter based on a distributed multi-transformer structure was presented in [12], [13] for hybrid renewable energy systems. However, the types of CFFB converters proposed in [10]-[13] use a greater number of transformers and switches, which increases the loss and cost of the overall system.

A conventional CFFB converter is shown in Fig. 1, which consists of a boost inductor, a full-bridge inverter with four switches, a high-frequency step-up transformer, a voltage double rectifier (VDR), and a load. When only a pair of switches ( $S_1$  and  $S_4$ ) or ( $S_2$  and  $S_3$ ) is turned "ON", the input current decreases and the converter operates in energy-transfer mode. When all switches are turned "ON", the input current increases and the converter operates in boost mode. The output voltage gain and the peak-to-peak inductor  $L_1$  current ripple of the conventional CFFB converter can be expressed as [20]:

Manuscript received June 23, 2016; revised October 26, 2016 and December 30, 2016; accepted February 26, 2017.

M.-K. Nguyen is with the Department of Electrical Engineering, Chosun University, Gwangju, 61452, Korea (e-mail: khainm@chosun.ac.kr, khaibk@ieee.org).

T.-D. Duong and Y.-C. Lim are with the Department of Electrical Engineering, Chonnam National University, Gwangju 500-757, Korea (e-mail: duyduong11141375@gmail.com and yclim@chonnam.ac.kr).

Y.-J. Kim is with the Department of Electrical Engineering, Chosun University, Gwangju, 61452, Korea (e-mail: kimyj21@chosun.ac.kr).

$$\begin{cases} V_{o} = \frac{2n}{1 - D_{c}} V_{g} \\ a\% = \frac{\Delta I_{L}}{I_{L}} = \frac{D_{c} T V_{g}^{2}}{2L_{1} P_{o}}, \end{cases}$$

(1)

where  $D_c$ , T, and n are the duty cycle when all switches are turned "ON", the switching period, and the turn ratio of the transformer, respectively.

The turning "ON" time interval of all switches is used to control the output voltage in conventional CFFB converters. Moreover, the current-fed converter generates a zero voltage at the primary side of the transformer when all switches are turned "ON". Therefore, the primary and secondary voltage waveforms of the high-frequency transformer vary according to when the period occurs for which all switches are "ON".

In this paper, a three-switch isolated boost DC-DC converter is proposed. Compared to the conventional CFFB converter, the proposed converter uses one less active switch, one extra diode, and one extra capacitor. The operating principles, analysis, and parameter design guidelines for the proposed converter are presented. To verify the analysis, results of the simulation and experiment are provided.

#### II. PROPOSED TOPOLOGY

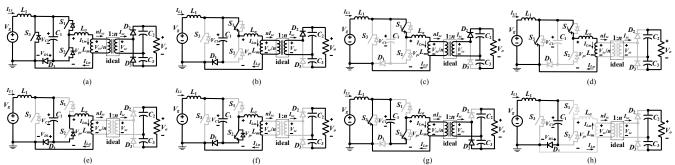

A circuit diagram of the proposed three-switch isolated boost DC-DC converter is shown in Fig. 2. The low-voltage side consists of a boost inductor  $(L_1)$ , three switches  $(S_1, S_2 \text{ and } S_3)$ , a capacitor  $(C_1)$ , a diode  $(D_1)$ , and the primary winding of the transformer (Tr). The high-voltage side consists of the load (R)and the secondary winding of the transformer (Tr) connected to the voltage double rectifier (VDR) implemented by two diodes  $(D_2 \text{ and } D_3)$  and two capacitors  $(C_2 \text{ and } C_3)$ . The main characteristics of the proposed converter are as follows: 1) the input DC current is continuous with low ripple, whereby a decoupling capacitor bank or an LC input filter at the front end (typically used to protect the energy source such as the fuel cell) is unnecessary; 2) it uses one less active switch, one extra diode and one extra capacitor than the conventional isolated boost DC-DC converter; 3) the primary and secondary side voltage waveforms of the high-frequency transformer are unchanged when the output voltage is controlled; this facilitates the ease of the design of the high-frequency transformer; and 4) the snubber circuit is not used because the voltage spike is limited by clamping the capacitor  $C_1$  voltage. As shown in Fig. 2, switch  $S_2$  in the proposed converter is now not connected to the source ground. Thus, three gate drivers with three separate grounds are used in the proposed converter. Compared to the conventional current-fed, four-switch, isolated boost DC-DC converter shown in Fig. 1 (in which four gate drivers with three separate grounds are used), both converters use the same number of separate grounds.

# A. Operating Principle

A circuit analysis of the proposed converter is performed under the following conditions: 1) the inverter operates in continuous conduction mode (CCM); 2) all devices are ideal

2

Fig. 2. Proposed three-switch, isolated boost DC-DC converter.

and lossless; 3) the high-frequency transformer is modeled by means of a leakage inductor connected to an ideal transformer; 4) the current flow to the windings of the transformer and the inductor increases or decreases linearly; 5) the capacitance of the capacitors is sufficient to maintain a constant capacitor voltage; 6) oscillations between the leakage inductance and parasitic capacitances are ignored; and 7)  $D_A$  is the minimum value of D, where D is the duty cycle of switch  $S_3$ .  $D_A$  is set to 0.3 in order to maintain the AC pulse primary and secondary side voltage waveforms of the high-frequency transformer at 30% positive, 20% zero, 30% negative, and 20% zero sequentially, respectively.  $D_A$  should be in the range of [0.25, 0.5] for the optimal utilization of the high-frequency transformer. The selection of  $D_A$  depends on the minimum voltage gain of the converter.

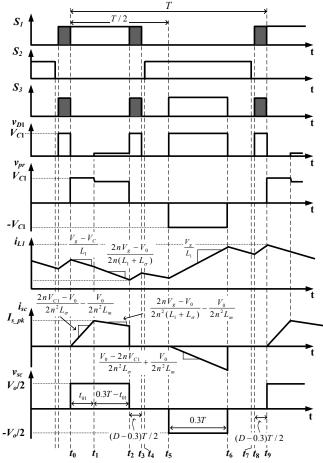

Fig. 3(a) shows the equivalent circuits of the proposed converter, in which the two windings of Tr are replaced by a leakage inductor  $(L_{\sigma})$  connected to an ideal transformer and a mutual inductance  $(L_m)$ . Fig. 4 shows the key waveforms of the proposed converter.

**Stage 1**– $[t_0 - t_1$ , Fig. 3(b)]:  $S_1$  is turned "ON", while  $S_2$  and  $S_3$  are turned "OFF". The inductor  $L_1$  is discharged, while the leakage inductor of the transformer and the capacitor are charged. The  $D_1$  and  $D_2$  diodes are forward-biased, while the  $D_3$  diode is reverse-biased. The primary voltage of the transformer is  $V_{c1}$ . The secondary side of the transformer generates a positive voltage. The time interval in this stage is  $t_{01}$ . We have:

$$L_{1} \frac{dt_{L1}}{dt} = V_{g} - V_{C1}$$

$$L_{\sigma} \frac{dt_{L\sigma}}{dt} = V_{C1} - \frac{V_{o}}{2n}$$

$$L_{m} \frac{dt_{Lm}}{dt} = \frac{V_{o}}{2n}.$$

(2)

The secondary current of the transformer increases linearly from zero to the peak value and is calculated by

$$i_{sc} = \frac{1}{2n^2} \left( \frac{2nV_{c1} - V_o}{L_\sigma} - \frac{V_o}{L_m} \right) t.$$

(3)

**Stage 2**–[ $t_1 - t_2$ , Fig. 3(c)]: when the primary winding current is charged to the inductor  $L_1$  current, the  $D_1$  diode is reverse-biased. The leakage inductor of the transformer is discharged. Because the leakage inductor of the transformer is changed from the stored energy state in stage 1 to the transferred energy state in stage 2, the primary voltage of the transformer is lower than  $V_{c1}$ . The secondary side of the transformer still generates a positive voltage. The time interval in this stage is  $(0.3 \cdot T - t_{01})$ , where *T* is the switching period. The secondary current of the transformer is expressed as

1:

Fig. 3. Proposed converter: (a) equivalent circuit and (b)-(h) operating stages.

$$i_{sc} = \frac{1}{2n^2} \left( \frac{2nV_g - V_o}{L_1 + L_\sigma} - \frac{V_o}{L_m} \right) t + I_{s_pk},$$

(4)

where  $I_{s_pk}$  is the peak value of the secondary current of the transformer.

Stage  $3-[t_2 - t_3]$ , Fig. 3(d)]: when the proposed converter requires a higher boost voltage, one further mode, as shown in Fig. 3(d), is applied. This mode is inserted into the zero states, where the winding voltages of the transformer are zero, such that the voltage waveforms of the transformer are unchanged. In this mode,  $S_1$  and  $S_3$  are turned "ON", while  $S_2$  is turned "OFF". The inductor  $L_1$  is charged. The primary winding of the transformer is short-circuited by  $S_1$  and  $S_3$ . All diodes are reverse-biased and the secondary voltage of the transformer is zero. The time interval in this stage is  $(D - 0.3) \cdot T$ , where D is the duty cycle of switch  $S_3$ , and  $D \ge 0.3$ . We have:

$$L_{1} \frac{di_{L1}}{dt} = V_{g}$$

$$L_{\sigma} \frac{di_{L\sigma}}{dt} = L_{m} \frac{di_{Lm}}{dt} = 0.$$

(5)

**Stage 4**– $[t_3 - t_4$ , Fig. 3(e)]: At  $t_3$ ,  $S_1$  and  $S_3$  are turned "OFF" and  $S_2$  remains turned "OFF". The inductor  $L_1$  current is freewheeling through  $D_1$ , while the primary winding current freewheels through the body diode of  $S_2$ . The time interval in this stage is very short.

**Stage 5**–[ $t_4 - t_5$ , Fig. 3(f)]: Because the current flows through the body diode of  $S_2$  at  $t_4$ , the direction of the current of  $S_2$ reverses and  $S_2$  is turned "ON" with zero-voltage switching (ZVS). The inductor  $L_1$  current freewheels through  $D_1$  and decreases linearly. The primary winding of the transformer is in a short-circuit situation through  $S_2$  and  $D_1$ . The secondary voltage of the transformer is zero, the  $D_2$  and  $D_3$  diodes are reverse-biased, and the primary current of the transformer is unchanged. We get:

$$\begin{bmatrix}

L_1 \frac{dl_{L1}}{dt} = V_g - V_{C1} \\

L_\sigma \frac{dl_{L\sigma}}{dt} = L_m \frac{dl_{Lm}}{dt} = 0.

\end{bmatrix}$$

(6)

**Stage 6**– $[t_5 - t_6$ , Fig. 3(g)]: At  $t_5 = T/2$ ,  $S_3$  is turned "ON", while  $S_1$  remains "OFF" and  $S_2$  remains "ON". The inductor  $L_1$  is charged, while the capacitor  $C_1$  is discharged. The primary voltage of the transformer is  $-V_{c1}$ . Also, the secondary voltage of the transformer is  $-nV_{c1}$ . The  $D_1$  and  $D_2$  diodes are reverse-biased, while the  $D_3$  diode is forward-biased. The time interval in this stage is  $0.3 \cdot T$ , and is the sum of the time

intervals in stages 1 and 2 to generate symmetrical AC waveforms at the primary side of the transformer. We get:

$$L_{1} \frac{dI_{L1}}{dt} = V_{g}$$

$$L_{\sigma} \frac{di_{L\sigma}}{dt} = -V_{C1} + \frac{V_{o}}{2n}$$

$$L_{m} \frac{di_{Lm}}{dt} = \frac{-V_{o}}{2n}.$$

(7)

The secondary current of the transformer is calculated by

$$i_{sc} = \frac{1}{2n^2} \left( \frac{-2nV_{C1} + V_o}{L_\sigma} + \frac{V_o}{L_m} \right) t.$$

(8)

**Stage** 7–[ $t_6 - t_7$ , Fig. 3(f)]: At  $t_6$ ,  $S_3$  is turned "OFF", while  $S_1$  remains "OFF" and  $S_2$  remains "ON". The converter operates as stage 5. The primary winding of the transformer is in a short-circuit situation through  $S_2$  and  $D_1$ , and the primary winding current then reduces to zero. The time intervals in stages 5 and 7 are equal  $(0.7 - D) \cdot T/2$ .

**Stage 8**–[ $t_7 - t_8$ , Fig. 3(h)]: At  $t_7$ , the current of  $S_2$  is zero, and  $S_2$  is turned "OFF" with zero-current switching (ZCS). The inductor  $L_1$  current still freewheels through  $D_1$ . The drain-source voltage of  $S_2$  increases from zero to  $V_{C1}$ , while the drain-source voltage of  $S_1$  decreases from  $V_{C1}$  to zero. The time interval in this stage is very short.

**Stage 9**–[ $t_8 - t_9$ , Fig. 3(d)]: At  $t_8$ , the drain-source voltage of  $S_1$  is zero and  $S_1$  is turned "ON" with ZVS. In this stage,  $S_2$  is turned "OFF" while  $S_1$  and  $S_3$  are turned "ON". The converter operates as stage 3. The time intervals in stages 3 and 9 are equal  $(D - 0.3) \cdot T/2$ .

As shown in Fig. 4, the transformer currents are not symmetric about their two halves, which are positive and negative. This could result in a deteriorated performance of the transformer in the proposed converter in comparison to that in the conventional full-bridge converters. Further, a small air gap is used to avoid the core saturation caused by the asymmetric transformer currents.

In the proposed converter, a capacitor  $C_1$  is placed between the input inductor and the leakage inductor of the transformer for removal of the snubber circuit. When the input inductor is changed from the stored energy state to the transferred energy state, the currents of the inductors do not change suddenly because the capacitor  $C_1$  links between the input inductor and the leakage inductor. Therefore, a snubber circuit is not needed in the proposed converter. However, because the  $S_3$  switch is

Fig. 4. Key waveforms of the proposed converter.

turned off with hard-switching, an over-stress voltage appears on  $S_3$ . As discussed in [14], the voltage rating of the primary switches in the isolated boost converter is typically rated at two to three times the maximum input voltage. Therefore, an acceptance over-stress on the  $S_3$  switch is less than three times the maximum input voltage. This over-stress depends on the stray inductances of the circuit and the slope of  $di_{DS3}/dt$ , where  $i_{DS3}$  is the drain-source current of  $S_3$ .

#### B. Voltage Conversion Ratio

Applying the volt-second balance law to the inductor  $L_1$ , in a steady state, (2), (5), (6), (7) yield:

$$V_{C1} = \frac{V_g - (0.3 - t_{01} / T) V_{D1}}{1 - D},$$

(9)

where  $V_{D1}$  is the diode  $D_1$  voltage in stage 2. As shown in Fig. 4,  $V_{D1}$  in stage 2 is very small in comparison with V<sub>g</sub>. Also, the value of  $(0.3 - t_{01}/T)$  is small. Therefore,  $V_{D1} \cdot (0.3 - t_{01}/T)$  is very small and can be neglected. The capacitor  $C_1$  voltage in (9) can be approximated as

$$V_{C1} \approx \frac{1}{1 - D} V_g. \tag{10}$$

Given  $t_0 = 0$ , from (2), the inductor  $L_1$  current and the primary current of the transformer are calculated using

$$\begin{cases} i_{L1} = \frac{V_g - V_{C1}}{L_1} t + \frac{P_o}{V_g} - \frac{D(D - 2D_A)T}{2(1 - D)L_1} V_g \\ i_{L\sigma} = \frac{2nV_{C1} - V_o}{2nL_\sigma} t - \frac{DT}{2nL_m} V_o, \end{cases}$$

(11)

where  $P_o$  is the output power.

At  $t_1$ , the inductor  $L_1$  current is equal to the primary current of the transformer. Substituting (10) into (11), we have:

$$t_{01} = \left(\frac{P_o}{V_g^2 T} - \frac{D(D-0.6)}{2(1-D)L_1} + \frac{DG}{2nL_m}\right) \frac{2n(1-D)TL_\sigma L_1}{2n(L_1 + L_\sigma D) - (1-D)L_1 G},$$

(12)

where  $G = V_o/V_g$  is the output voltage gain. The ratio of the stage-one time interval to the positive-stage time interval is defined by

$$k = \frac{t_{01}}{t_{02}} = \frac{t_{01}}{0.3T} \le 1.$$

<sup>(13)</sup>

Substituting  $t_{01}$  in (12) into (3), the peak value of the secondary current of the transformer is

$$I_{s_{-}pk} = \frac{1}{2n^2} \left( \frac{2nV_{C1} - V_o}{L_{\sigma}} - \frac{V_o}{L_m} \right) t_{01}.$$

(14)

From (3), (4), and (8), the average secondary current of the transformer is calculated as

$$\overline{i}_{sc} = \frac{1}{T} \begin{bmatrix} \frac{1}{2n^2} \left( \frac{2nV_{C1} - V_o}{L_\sigma} - \frac{V_o}{L_m} \right) \frac{t_{01}^2}{2} \\ + \frac{1}{2n^2} \left( \frac{2nV_g - V_o}{L_1 + L_\sigma} - \frac{V_o}{L_m} \right) \frac{\left(0.3T - t_{01}\right)^2}{2} \\ + I_{s_-pk} \frac{0.3T - t_{01}}{T} + \frac{1}{2n^2} \left( \frac{2nV_{C1} - V_o}{L_\sigma} - \frac{V_o}{L_m} \right) \frac{\left(0.3T\right)^2}{2} \end{bmatrix}.$$

(15)

Substituting  $I_{s,pk}$  in (14) into (15), and simplifying it, we get

$$\bar{t}_{sc} = \frac{T}{4n^2} \begin{bmatrix} \left(\frac{2nV_g - V_o}{L_1 + L_\sigma} - \frac{2nV_{C1} - V_o}{L_\sigma} - \frac{2V_o}{L_m}\right) \left(\frac{t_{01}}{T}\right)^2 \\ +0.06 \left(\frac{2nV_{C1} - V_o}{L_\sigma} - \frac{2nV_g - V_o}{L_1 + L_\sigma}\right) \frac{t_{01}}{T} \\ +0.09 \left(\frac{2nV_g - V_o}{L_1 + L_\sigma} + \frac{2nV_{C1} - V_o}{L_\sigma} - \frac{2V_o}{L_m}\right) \end{bmatrix}.$$

(16)

Because the leakage inductor  $(L_{\sigma})$  is very small in comparison with the input inductor  $(L_1)$  and the mutual inductance  $(L_m)$ , the average secondary current of the transformer in (16) is approximated as

$$\overline{i}_{sc} \approx \frac{2nV_{C1} - V_o}{4n^2 L_o} \left( 0.09 + 0.06 \frac{t_{01}}{T} - \left(\frac{t_{01}}{T}\right)^2 \right).$$

(17)

Because a voltage double rectifier (VDR) is used in the proposed converter, the average secondary current of the transformer is two times the load current ( $\overline{i_{sc}} = 2I_o$ ). Substituting V<sub>c1</sub> in (10) and  $t_{01} = 0.3k \cdot T$  in (13) into (17), we get:

$$G = \frac{V_o}{V_g} \approx \frac{2n}{1 - D} - \varepsilon, \tag{18}$$

where  $\varepsilon = \frac{8n^2 L_{\sigma} I_o}{0.09(1+2k-k^2)TV_g}$

From (18), it can be observed that the output voltage gain is controlled by D. Note that (18) is not a closed-form expression

because *G* depends on *k*, but *k* depends on *G* according to (12). However, the effect of *k* on the DC voltage gain in the circuit design is insignificant because  $\varepsilon$  in (18) is very small in comparison to 2n/(1-D).

## C. Pulse-Width-Modulation (PWM) Control

Fig. 4 also shows the pulse-width-modulation (PWM) control method for the proposed converter. In this PWM control method, the extra state, where  $S_1$  and  $S_3$  are turned "ON" simultaneously, is inserted into the zero state to extend the period for which  $S_1$  is "ON" continuously. The reference voltage,  $V_{ref}$  is compared to a high-frequency triangle waveform,  $V_{tri}$  to generate the control signals for the  $S_3$  switch. Another reference voltage with amplitude of  $(1-V_{ref})$  is compared to  $V_{tri}$  to generate the control signals for the  $S_1$  and  $S_2$  switches. To generate the extra states, the control voltage,  $V_{con}$  is compared to  $V_{tri}$ . Note that  $V_{con}$  is in the range of  $[1-V_{ref}, V_{ref}]$  to ensure that the extra state is only inserted into the zero state. In the proposed converter,  $V_{ref}$  is normally kept constant for the unchanging voltage of the proposed converter is only  $V_{con}$ .

## D. Voltage and Current Stresses

The capacitor  $C_1$  voltage stress is approximated in (10). The voltage stress of the  $S_1 - S_3$  switches, the  $D_1$  diode, and the transformer primary side are equal to the capacitor  $C_1$  voltage stress. The voltage stress of the  $C_2$  and  $C_3$  capacitors is half of the output voltage, while the voltage stress of the  $D_2$  and  $D_3$  diodes is equal to the output voltage.

To easily derive the current stress of the  $D_1$  diode, we ensure that the inductor current is taken as constant with a free ripple. The inductor current is the input current and is equal to  $P_o/V_g$ , where  $P_o$  is the output power. The diode  $D_1$  current can be expressed as

$$i_{D1} = \begin{cases} -\frac{P_o}{V_g t_{01}} t + \frac{P_o}{V_g}, & 0 < t < t_1 \\ P_o / V_g, & t_3 < t < t_5 \text{ and } t_6 < t < t_8 \\ 0, & \text{other time intervals.} \end{cases}$$

(19)

The RMS current of the  $D_1$  diode is given by

$$I_{RMS_{D1}} = \frac{P_o}{V_g} \sqrt{0.7 - D + t_{01} / (3T)}.$$

(20)

From (10) and (20), the stresses on the elements depend on the existence of an extra stage. Because the effect of k on the DC voltage gain is insignificant, we can set k = 0.5 in the circuit design. Next, the maximum duty cycle  $(D_{max})$  of  $S_3$  is calculated from (18) based on the maximum DC voltage gain. Then, the stresses on the elements are calculated based on  $D_{max}$ .

## III. PARAMETER DESIGN OF THE INDUCTOR AND CAPACITOR

# A. Parameter Design of the Inductor

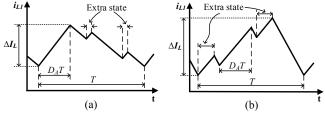

Different PWM control conditions cause varying input current ripples in the proposed converter. The inductor is designed based on the peak-to-peak current ripple passing

Fig. 5. Inductor  $L_1$  current ripple. (a) D < 0.5 and (b) D > 0.5.

through to the inductor. Fig. 5 shows the peak-to-peak current ripple of the  $L_1$  inductor using the PWM control method presented in Section II. C. When D < 0.5, the peak-to-peak inductor  $L_1$  current is calculated based on stage 6, in which the secondary voltage is negative. When  $D \ge 0.5$ , the peak-to-peak inductor  $L_1$  current is calculated based on stages 1 and 2, in which the secondary voltage is positive. From (2) and (6), the peak-to-peak inductor  $L_1$  current is

$$\Delta I_{L} = \begin{cases} \frac{0.3TV_{g}}{L_{1}}, & D < 0.5\\ \frac{0.3DTV_{g}}{(1-D)L_{1}}, & D \ge 0.5. \end{cases}$$

(21)

The input current ripple of the proposed converter is calculated as

$$a\% = \frac{\Delta I_{L}}{I_{L}} = \begin{cases} \frac{0.3TV_{g}^{2}}{L_{1}P_{o}}, & D < 0.5\\ \frac{0.3DTV_{g}^{2}}{(1-D)L_{1}P_{o}}, & D \ge 0.5. \end{cases}$$

(22)

Comparing (22) to (1), the input current ripple of the proposed converter is two times higher than that of the conventional converter.

If the inductor current ripple  $\Delta I_L$  is chosen such that  $\Delta I_L \leq a\% I_L$ , the required  $L_1$  inductance should be

$$L_{1} = \begin{cases} \frac{0.3TV_{g}^{2}}{a\% P_{o}}, & D < 0.5\\ \frac{0.3DTV_{g}^{2}}{(1-D)a\% P_{o}}, & D \ge 0.5. \end{cases}$$

(23)

## B. Parameter Design of the Capacitor

The capacitors are designed according to the capacitor voltage ripple. The current flow to the  $C_1$  capacitor in the negative mode of the proposed converter, as shown in Fig. 3(g), can be rewritten as

$$C_1 \frac{\Delta V_{C1}}{D_A T} = n \overline{i_{sc}}.$$

(24)

If the peak-to-peak capacitor voltage ripple is limited passing through by b%, the capacitance for  $C_l$  in the proposed converter should be

$$C_1 = \frac{0.3(1-D)^2 T P_o}{b\% V_o^2}.$$

(25)

Because the slope of  $di_{DS3}/dt$  affects the peak-to-peak capacitor voltage ripple, the selection of capacitance  $C_1$  in (25) compensates for the effect of the over-stress on the  $S_3$  switch.

The output capacitors ( $C_2$  and  $C_3$ ) of the VDR are selected as follows. When the converter is in zero mode, as shown in Figs. 3(d) and 3(f), the  $C_2$  and  $C_3$  capacitor currents, respectively, are equal to the negative load current. To limit the ripple on the output voltage at c%, the capacitance should be

$$C_2 = C_3 = \frac{0.4(1-D)^2 T P_o}{4c\% n^2 V_g^2}.$$

(26)

# IV. SIMULATION AND EXPERIMENTAL RESULTS

## A. Simulation Results

To verify the operating principle of the proposed converter shown in Fig. 2, PSIM simulation was performed with the following parameters:  $L_1 = 1$  mH,  $C_1 = 220 \mu$ F,  $C_2 = C_3 = 150 \mu$ F, and  $R = 600 \Omega$ . The drain-to-source on-resistance of metal-oxide-semiconductor field-effect transistors (MOSFETs) was set to 8 m $\Omega$ . The forward voltage of the diodes was set to 0.7 V. The turn ratio of the high-frequency transformer was 2.5. The magnetic inductance measured from the primary side was set to 1.4 mH. The leakage inductance was set to 11  $\mu$ H. The switching frequency was 10 kHz and the output voltage was 400 V. The deadtime between  $S_1$  and  $S_2$  is 2  $\mu$ s. Table I shows the simulation parameters for the proposed three-switch isolated boost converter.

TABLE I SIMULATION AND EXPERIMENTAL PARAMETERS OF PROPOSED CONVERTER

| Input voltage range $(V_g)$ |                    | 40 - 60 V |

|-----------------------------|--------------------|-----------|

| Output voltage $(V_o)$      |                    | 400 V     |

| Inductor $(L_1)$            |                    | 1 mH      |

| Transformer                 | Turn ratio         | 1:2.5     |

|                             | Primary inductance | 1.4 mH    |

|                             | Leakage inductance | 11 µH     |

| Capacitors                  | $C_1$              | 220 µF    |

|                             | $C_2 = C_3$        | 150 μF    |

| Switching frequency         |                    | 10 kHz    |

| Resistive load ( <i>R</i> ) |                    | 600 Ω     |

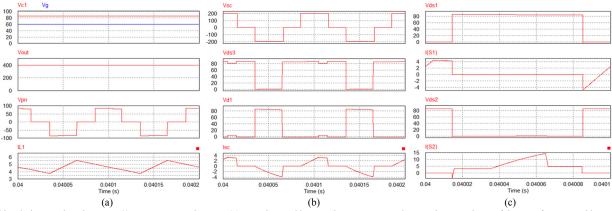

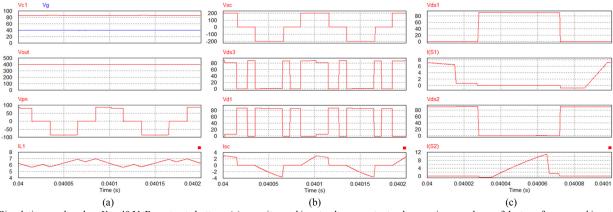

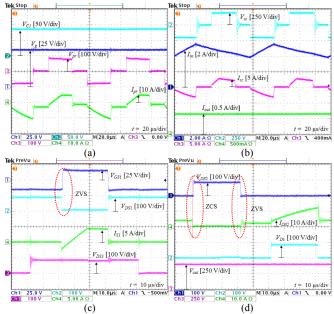

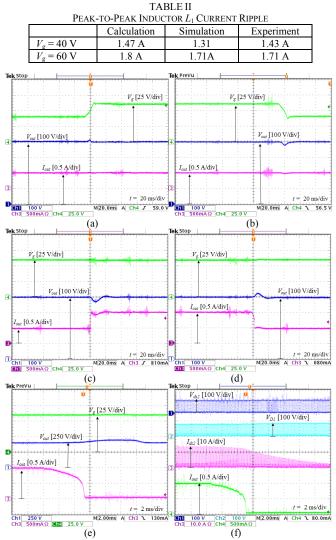

Fig. 6 shows the simulation results for the proposed converter when  $V_g = 60$  V. The input current is continuous, with a peak-to-peak ripple of 1.71 A. The primary voltage of the transformer has three levels. Fig. 7 shows the simulation results for the proposed converter when  $V_g = 40$  V. The input current is continuous, with a peak-to-peak ripple of 1.31 A. The primary and secondary voltage waveforms of the transformer shown in Fig. 7(a) are the same as those shown in Fig. 6(a). As shown in Fig. 7, an extra mode is applied to the zero state to boost the voltage when a minimum input voltage is used. Therefore, the primary and secondary voltage waveforms of the transformer are unchanged, even though the input voltage changes from maximum to minimum. These simulation results are in agreement with the theoretical analysis.

Fig. 6. Simulation results when  $V_g = 60$  V. From top to bottom: (a) capacitor and input voltages, output voltage, primary voltage of the transformer, and input current; (b) secondary voltage of the transformer, drain–source voltage of  $S_3$ , diode  $D_1$  voltage, and secondary current of the transformer; and (c) drain–source voltage of  $S_1$ , drain–source current of  $S_2$ .

Fig. 7. Simulation results when  $V_g = 40$  V. From top to bottom: (a) capacitor and input voltages, output voltage, primary voltage of the transformer, and input current; (b) secondary voltage of the transformer, drain–source voltage of  $S_3$ , diode  $D_1$  voltage, and secondary current of the transformer; and (c) drain–source voltage of  $S_1$ , drain–source current of  $S_2$ .

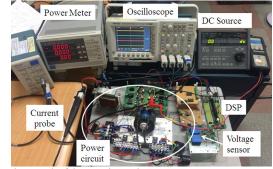

Fig. 8. Photograph of the experimental setup.

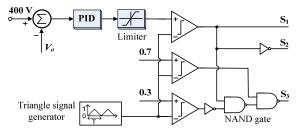

Fig. 9. Output voltage control algorithm for the proposed converter.

#### B. Experimental Results

A 400 W laboratory prototype based on a TMS320F28335 DSP was built to verify the properties of the proposed three-switch isolated boost DC-DC converter. Fig. 8 shows the experimental setup in the laboratory. The same parameters as those in the simulation were used. The  $C_1$  capacitor is 220  $\mu$ F/ 450 V. Two 150  $\mu$ F/ 450 V capacitors were used for  $C_2$  and  $C_3$ . The  $L_1$  inductor was 1 mH/ 20 A (Changsung Corp.). The transformer utilized a B65686 N27 core (EPCOS). The primary windings had 38 turns, while the secondary windings had 95 turns. The magnetic inductance measured from the primary side was 1.4 mH. The leakage inductance measured at the primary winding by shorting the second winding was 11 µH. Three IRFP4668PbF MOSFETs and one STPS60SM200C Schottky diode were used on the primary side, while two DSEP30-12A diodes were used on the secondary side. The deadtime between  $S_1$  and  $S_2$  is 2 µs.

To maintain the output voltage at 400 V, a proportional-integral-derivative (PID) voltage controller is used as shown in Fig. 9. The error signal between the output voltage sensor and the reference value of 400 V is passed over the PID controller. The PID control output is limited to the range of [0.3, 0.7]. This control value is used to generate the control signals of  $S_1$  and  $S_2$ . To generate the control signal of  $S_3$ , reference voltages of 0.3 and 0.7 V are compared to the high-frequency triangle waveform. Two NAND logic gates are used to insert the zero state into  $S_3$ .

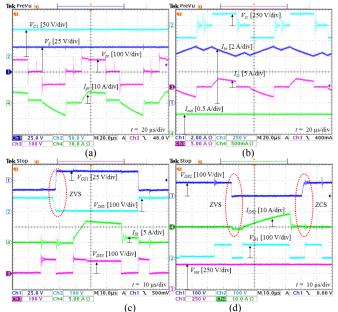

Fig. 10 shows the experimental results for the proposed converter when the maximum input voltage of 60 V was used at the output power of 266 W. An extra mode, in which both  $S_1$  and  $S_3$  are turned "ON", was not applied to the switching state, and D = 0.3. The calculated capacitor  $C_1$  voltage from (10) was approximately 86 V when  $V_g = 60$  V and D = 0.3. The measured value of the capacitor  $C_1$  voltage was 85 V.

Fig. 10. Experimental voltage waveforms of the proposed converter when  $V_g = 60$  V at the output power of 266 W.

Fig. 11. Experimental voltage waveforms of the proposed converter when  $V_g = 40$  V at the output power of 266 W.

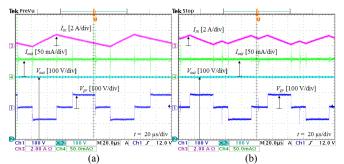

Fig. 12. Experimental results with light load (5.8% of full load) (a)  $V_g = 60$  V and (b)  $V_g = 40$  V.

Fig. 11 shows the experimental results for the proposed converter when the minimum input voltage of 40 V is used at the output power of 266 W. An extra mode was inserted into the zero state of the converter. The duty cycle of  $S_3$  in this case was 0.55. The measured value of the capacitor  $C_1$  voltage was 87 V, while the calculated value from (10) was approximately 89 V. The capacitor  $C_1$  voltage in the simulation and experiment was always lower than the calculated value due to the parasitic effect of the components.

In Figs. 10(a) and 11(a), the waveforms from top to bottom are the capacitor  $C_1$  voltage, input voltage, primary voltage, and primary current. In Figs. 10(b) and 11(b), the waveforms from top to bottom are the secondary voltage, input current, secondary current, and output current. In Figs. 10(c) and 11(c), the waveforms from top to bottom are the gate-source voltage, the drain-source voltage of  $S_1$ , the drain-source current of  $S_1$ , and the drain-source voltages of  $S_3$ . In Figs. 10(d) and 11(d), the waveforms from top to bottom are the drain-source voltage of  $S_2$ , the current of  $S_2$ , the diode  $D_1$  voltage, and the output voltage. As shown in Figs. 10 and 11, the  $S_1$  and  $S_2$  switches are turned on with ZVS, and the  $S_2$  switch is turned off with ZCS.

Table II compares the peak-to-peak inductor  $L_1$  current in the simulation and experiment to that in the theory in (16). The experimental results differ only slightly from the theoretical and simulation results.

Fig. 12 shows the experimental result of the proposed converter with light load (5.8% of full load). As shown in Fig. 12, the input current is continuous when a very light load is used. Fig. 13 shows the dynamic response of the proposed converter under a PID controller. In Fig. 13(a), the input voltage is changed from 40 V to 60 V while the resistive load is kept at 800  $\Omega$ . In Fig. 13(b), the input voltage is changed from 60 V to 40 V, while the resistive load is kept at 800  $\Omega$ . In Fig. 13(c), the input voltage is kept constant at 60 V while the load is changed from 50% load (800  $\Omega$ ) to full load (400  $\Omega$ ). In Fig. 13(d), the input voltage is kept constant at 60 V, while the load is changed from full load to 50% load. In Figs. 13(e) and 13(f), the input voltage is kept constant at 60 V while the load is changed from full load (400  $\Omega$ ) to light load (5.8% of full load). In Figs. 13(a)-13(e), the waveforms from top to bottom are the input voltage, the output voltage, and the output current. The transient stress on the components when the load is changed from full load to light load is shown in Fig. 13(f). In Fig. 13(f), the waveforms from top to bottom are the drain-source voltage stress of the  $S_2$  switch, the diode  $D_1$  voltage stress, the drain-source current stress of the  $S_2$  switch, and the output current. In Fig. 13, the output voltage is kept at 400 V, despite the change in the input voltage or load.

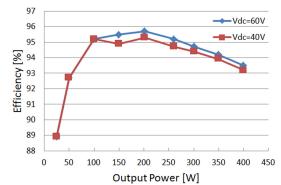

Fig. 14 shows the measured efficiency of the proposed converter under different operating conditions. The proposed converter reaches a maximum efficiency of 95.7% when the maximum input voltage is used. The efficiency is reduced when the input voltage is decreased to 40 V. This is due to the increased switching loss of  $S_3$  and high conduction loss in the devices when a higher boost voltage is required. The measured efficiency of the proposed converter at the very light load is 88.9% when the input voltage is 40 V and 60 V. Compared to the conventional converters, the efficiency of the proposed

Fig. 13. Experimental results with (a) input voltage change from 40 V to 60 V, (b) input voltage change from 60 V to 40 V, (c) load change from half load to full load, (d) load change from full load to half load, (e) and (f) load change from full load to light load (5.8% full load).

Fig. 14. Measured efficiency vs. output power of the proposed converter.

converter is not high. This is because both the  $S_1$  and  $S_3$  switches of the proposed converter are switched off with hard-switching. Moreover, the test conditions are not the optimal operation conditions, where the inductor, capacitors, and high-frequency transformer are not well designed.

# V. CONCLUSIONS

A new three-switch isolated boost DC-DC converter was proposed in this paper. The proposed converter has the following characteristics: continuous input current, reduced one active switch, unchanged primary and secondary voltage waveforms of the transformer, and no snubber circuit. The limitations of the proposed converter compared to the conventional CFFB converter are as follows: one extra diode and one extra capacitor are used, a higher input current ripple is needed, and it is operated in hard-switching. The operating principles, analysis, parameter design guidelines, and simulation results are presented. A laboratory prototype with a PID controller was constructed to verify the operating theory of the proposed converter. The proposed converter is applicable for fuel-cell applications in which a varying low-dc input voltage is boosted to a high fixed dc output voltage with a continuous input current and galvanic isolation.

#### References

- [1] D. S. Gautam, F. Musavi, W. Eberle, and W. G. Dunford, "A zero-voltage switching full-bridge dc-dc converter with capacitive output filter for plug-in hybrid electric vehicle battery charging," *IEEE Trans. Power Electron.*, vol. 28, no. 12, pp. 5728–5735, Dec. 2013.

- [2] Y. Xie, R. Ghaemi, J. Sun, and J. S. Freudenberg, "Implicit model predictive control of a full bridge dc-dc converter," *IEEE Trans. Power Electron.*, vol. 24, no. 12, pp. 2704–2713, Dec. 2009.

- P. Sun, L. Zhou, and K. M. Smedley, "A reconfigurable structure dc–dc converter with wide output range and constant peak power," *IEEE Trans. Power Electron.*, vol. 26, no. 10, pp. 2925-2935, Oct. 2011.

B. Gu, J. S. Lai, N. Kees, and C. Zheng, "Hybrid-switching full-bridge

- [4] B. Gu, J. S. Lai, N. Kees, and C. Zheng, "Hybrid-switching full-bridge dc-dc converter with minimal voltage stress of bridge rectifier, reduced circulating losses, and filter requirement for electric vehicle battery chargers," *IEEE Trans. Power Electron.*, vol. 28, no. 3, pp. 1132–1144, March 2013.

- [5] C. Yao, X. Ruan, and X. Wang, "Isolated buck-boost dc/dc converters suitable for wide input-voltage range," *IEEE Trans. Power Electron.*, vol. 26, no. 9, pp. 2599–2613, Sep. 2011.

- [6] C. Yao, X. Ruan, and X. Wang, "Automatic mode-shifting control strategy with input voltage feed-forward for full-bridge-boost dc-dc converter suitable for wide input voltage range," *IEEE Trans. Power Electron.*, vol. 30, no. 3, pp. 1668–1682, March 2015.

[7] H. Wu, Y. Lu, K. Sun, and Y. Xing, "Phase-shift controlled isolated

- [7] H. Wu, Y. Lu, K. Sun, and Y. Xing, "Phase-shift controlled isolated buck-boost converter with active-clamped three-level rectifier (AC-TLR) featuring soft-switching within wide operation range," *IEEE Trans. Power Electron.*, vol. 31, no. 3, pp. 2372-2386, Mar. 2016.

- [8] R. Y. Chen, T. J. Liang, J. F. Chen, R. L. Lin, and K. C. Tseng, "Study and implementation of a current-fed full-bridge boost dc-dc converter with zero-current switching for high-voltage applications," *IEEE Trans. Ind. Appl.*, vol. 44, no. 4, pp. 1218-1226, July/Aug. 2008.

- [9] S. Jalbrzykowski and T. Citko, "Current-fed resonant full-bridge boost dc/ac/dc converter," *IEEE Trans. Ind. Electron.*, vol. 55, no. 3, pp. 1198-1205, March 2008.

- [10] X. Kong, and A. M. Khambadkone, "Analysis and implementation of a high efficiency, interleaved current-fed full bridge converter for fuel cell system," *IEEE Trans. Power Electron.*, vol. 22, no. 2, pp. 543–550, March 2007.

- [11] A. Mohammadpour, L. Parsa, M. H. Todorovic, R. Lai, R. Datta, and L. Garces, "Series-input parallel-output modular-phase dc-dc converter with soft-switching and high-frequency isolation," *IEEE Trans. Power Electron.*, vol. 31, no. 1, pp. 111–119, Jan. 2016.

- [12] Z. Zhang, O. C. Thomsen, M. A. E. Andersen, and H. R. Nielsen, "Dual-input isolated full-bridge boost dc-dc converter based on the distributed transformers," *IET Power Electron.*, vol. 5, no. 7, pp. 1074–1083, Aug. 2012.

- [13] Z. Zhang, O. C. Thomsen, and M. A. E. Andersen, "Soft-switched dual-input dc-dc converter combining a boost-half-bridge cell and a

voltage-fed full-bridge cell," *IEEE Trans. Power Electron.*, vol. 28, no. 11, pp. 4897–4920, Nov. 2013.

- [14] M. Nymand, and M. A. E. Andersen, "High-efficiency isolated boost dc-dc converter for high-power low-voltage fuel-cell applications," *IEEE Trans. Ind. Electron.*, vol. 57, no. 2, pp. 505-514, Feb. 2010.

- [15] Z. Lizhi "A novel soft-commutating isolated boost full-bridge ZVSPWM dc-dc converter for bidirectional high power applications," *IEEE Trans. Power Electron.*, vol. 21, no. 2, pp. 422–429, Feb. 2006.

[16] A. Mousavi, P. Das, and G. Moschopoulos, "A comparative study of a

- [16] A. Mousavi, P. Das, and G. Moschopoulos, "A comparative study of a new ZCS dc-dc full-bridge boost converter with a ZVS active-clamp converter," *IEEE Trans. Power Electron.*, vol. 27, no. 3, pp. 1347–1358, March 2012.

- [17] U. R. Prasanna, and A. K. Rathore, "Extended Range ZVS Active-Clamped Current-Fed Full-Bridge Isolated DC/DC Converter for Fuel Cell Applications: Analysis, Design, and Experimental Results," *IEEE Trans. Ind. Electron.*, vol. 60, no. 7, pp. 2661-2672, July 2013.

- [18] M. Baei, M. Narimani, and G. Moschopoulos, "A new ZVS-PWM full-bridge boost converter," *Journal of Power Electronics*, vol. 14, no. 2, pp. 237-248, March 2014.

- [19] M. Mohr, and F. W. Fuchs, "Clamping for current-fed dc/dc converters with recovery of clamping energy in fuel cell inverter systems," in *Proc. European Conf. Power Electron. and Applicat. (EPE)*, 2-5 Sept. 2007, pp. 1-10.

- [20] P. Xuewei, A. K. Rathore, and U. R. Prasanna, "Novel soft-switching snubberless naturally clamped current-fed full-bridge front-end-converter-based bidirectional inverter for renewables, microgrid, and UPS applications," *IEEE Trans. Ind. Appl.*, vol. 50, no. 6, pp. 4132-4141, Nov/Dec. 2014.

- [21] P. Xuewei, and A. K. Rathore, "Novel bidirectional snubberless naturally commutated soft-switching current-fed full-bridge isolated dc/dc converter for fuel cell vehicles," *IEEE Trans. Ind. Electron.*, vol. 61, no. 5, pp. 2307-2315, May 2014.

**Minh-Khai Nguyen** (S'09–M'12) received the B.S. degree in electrical engineering from the Ho Chi Minh City University of Technology, Ho Chi Minh City, Vietnam, in 2005, and the M.S. and Ph.D. degrees in electrical engineering from Chonnam National University, Gwangju, South Korea, in 2007 and 2010, respectively. From 2010 to 2013, he was a Lecturer with Nguyen Tat Thanh University, Ho Chi Minh City. Since 2013, he has been a Lecturer with the Ho Chi Minh City University of Technology and

Education, Ho Chi Minh City. Since 2016, he has been an Assistant Professor with Chosun University, Gwangju. His current research interests include renewable energy systems, power quality, and power converters.

**Truong-Duy Duong** received the B.S degree in Electronic Telecommunication Engineering from the Ho Chi Minh City University of Technology and Education, Ho Chi Minh city, Viet Nam, in 2015. He is currently working toward the M.S. degree in the Department of Electrical Engineering, Chonnam National University, Gwangju, Korea. His research interests include topology and control of soft-switching dc-dc converter.

Young-Cheol Lim (M'85) was born in Chonnam Province, South Korea, in 1953. He received the B.S. degree in electrical engineering from Chonnam National University, Gwangju, South Korea, in 1975, and the M.S. and Ph.D. degrees from Korea University, Seoul, South Korea, in 1977 and 1990, respectively.

In 1981, he became a Professor at Chonnam National University, where he was the Director of the Research Center for High-Quality Electric

Components and Systems from 1998 to 2007. He is the coauthor of three books. He has authored or coauthored more than 200 published technical papers. His current research interests include power electronics, control instruments, and neurofuzzy control. Dr. Lim was the President of the Korea Institute of Power Electronics (KIPE) in 2009. He has been involved in various academic societies, such as the KIPE, the Korean Institute of Electrical Engineers, and the Institute of Control, Automation, and Systems Engineers, South Korea. He has received a number of awards, including the 2000 KIPE Best Paper Award, and 2001 KIPE Academic Award.

Yong-Jae Kim (S'04-M'07) was born in Gwnagju, Korea, in 1973. He received the B. Eng. degree in electrical engineering from Chosun University, Gwangju Korea, in 1996 and the M. Eng. and Dr. Eng. degrees in electrical and electronic engineering from Musashi Institute of Technology, Tokyo, Japan, in 2003 and 2006, respectively. He was a Researcher of Electrical and Electronic Engineering at Musashi Institute of Technology, Tokyo, Japan, from 2006 to 2007. He is currently an Associate Professor with the

Department of Electrical Engineering, Chosun University, Gwnagju, Korea. His current research interests include the design and the numerical analysis of electric machines and AC servo drive systems.