# Investigation on the Ripple Voltage and the Stability of SR Buck Converters With High Output Current and Low Output Voltage

Masahito Jinno, Po-Yuan Chen, Yu-Chun Lai, and Koosuke Harada, Fellow, IEEE

Abstract—Synchronous rectifiers (SRs) composed of MOSFETs have recently been employed to replace the conventional rectifiers with diodes. SRs are widely used in switched-mode power supplies with low output voltage and high output current for efficiency improvement. Owing to the high-efficiency characteristic, it is adequate to use an SR buck converter in a voltage regulator for powering a central processing unit. Normally, such SR buck converter must operate at fairly high switching frequency for miniaturizing a whole circuit and achieving a fast response. However, at the conditions of low output voltage, high output current, and high switching frequency, the influence of parasitic elements to circuit operation will become extremely obvious. Therefore, the design considerations concerning the ripple voltage and the stability of such SR converters should be carefully investigated and clarified. By establishing the equivalent circuit and using a state-space averaged method, the ripple ratio of output voltage and the static and dynamic characteristics of the SR buck converter with nonnegligible parasitic elements are obtained. Thus, the design criteria concerning the output ripple voltage and the stability are clarified.

${\it Index\ Terms} {\it --} Ripple\ ratio, stability, synchronous\ rectifier\ (SR), voltage\ regulator.$

# I. INTRODUCTION

WING TO the miniaturization of electronic products, the switched-mode power supplies (SMPSs) for these electronic products are required to become smaller. In order to realize the miniaturization of the SMPSs, the switching frequency should be raised properly before the adverse effect of miniaturization appears. However, at high switching frequency, the influence of parasitic elements [such as the equivalent series resistance (ESR) of output capacitor, the equivalent series inductance (ESL) of output capacitor, etc.] will not be negligible. In addition, with the development of the integration technology, the power requirement of most microprocessors tends to be high current and low voltage [1]–[5].

Thus, the power supplies for the microprocessors will be forced to face the combined conditions of high switching frequency, low output voltage, and high output current, which will extremely enhance the influence of the parasitic elements. In particular, for the synchronous rectifier (SR) buck converters [6]–[28], which are used in voltage regulator for supplying

Manuscript received January 13, 2009; revised July 29, 2009. First published August 18, 2009; current version published February 10, 2010.

M. Jinno, P.-Y. Chen, and Y.-C. Lai are with the Department of Electrical Engineering, I-Shou University, Dashu Township, Kaohsiung County 840, Taiwan (e-mail: jinno@isu.edu.tw; macoxd@gmail.com; laiujun@hotmail.com).

K. Harada is with the Energy Electronics Laboratory, Sojo University, Kumamoto 860, Japan (e-mail: harada@cis.sojo-u.ac.jp).

Digital Object Identifier 10.1109/TIE.2009.2029510

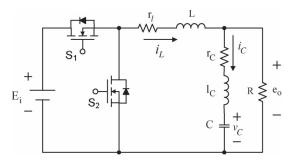

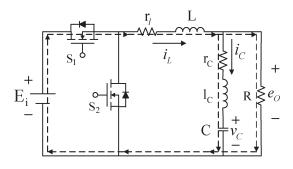

Fig. 1. Buck converter with SR.

power to a central processing unit (CPU), the operation conditions are extremely severe. In order to power a CPU, these converters are normally designed with the conditions of high switching frequency (500 kHz–1 MHz), very low output voltage (1.0–1.5 V), and very high output current (80–100 A).

Generally, most research topics regarding such SR buck converters are focused on the efficiency improvement and control method. However, this paper presents a unique point of view to link the ripple ratio of the output voltage and the stability by investigating the effects of the parasitic elements. In this paper, the effects of the parasitic elements on the output ripple voltage and the stability of the SR buck converter are analyzed and clarified. Moreover, several useful design considerations concerning the output ripple voltage and the stability are well summarized.

# II. EFFECTS OF THE PARASITIC ELEMENTS ON THE RIPPLE RATIO OF OUTPUT VOLTAGE

Fig. 1 shows an SR buck converter with SR, which can be used for powering a CPU. Due to the very low input voltage of the CPU, the output ripple voltage of the SR buck converter becomes an important issue.

Usually, an output capacitance is usually forced to be increased for suppressing the output ripple voltage. Although, theoretically, the output voltage ripple will decrease with the increase of the output capacitance, a minimum value of ripple voltage will exist practically. This minimum value is caused by the effects of the output capacitor's ESR and ESL.

## A. Derivation of Output Ripple Ratio

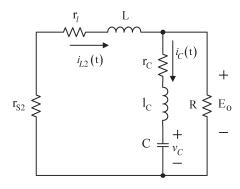

When  $S_1$  is in OFF state and  $S_2$  is in ON state, the equivalent circuit of Fig. 1 is shown in Fig. 2. In Fig. 2, L and C represent the output inductance and output capacitance, respectively;  $r_{S_2}$ ,

Fig. 2. Equivalent circuit of the SR buck converter ( $S_1$  OFF;  $S_2$  ON).

Fig. 3. Equivalent circuit for shunt mechanism.

$r_l$ ,  $r_C$ , R, and  $l_C$  represent the ON resistance of  $S_2$ , the spurious resistance of output inductor, the ESR of output capacitor, load resistance, and the ESL of output capacitor, respectively; and  $i_{L2}$  and  $E_O$  represent the instantaneous value of the current flowing through  $S_2$  and the averaged value of the output voltage  $e_O$ , respectively.

For the condition of large output capacitance (for the experimental prototype used in the research, the large output capacitance can be regarded as no less than  $2000~\mu\text{F}$ ), the output voltage  $e_O$  in Fig. 1 can be assumed as a constant value  $E_O$  in Fig. 2; thus, the circuit equation of  $i_{L2}$  can be expressed by

$$i_{L2}(t) = I_L^* e^{-\left(\frac{r_2}{L}\right)t} - \frac{1}{r_2} \left(1 - e^{-\left(\frac{r_2}{L}\right)t}\right) E_O$$

(1)

where  $I_L^*$  represents the initial value of  $i_{L2}$ , and  $r_2 = r_{S2} + r_l$ . Under high switching frequency condition, the ripple current of output inductor can be obtained as

$$\Delta I_L = \frac{D'T_S E_O}{L} \left( 1 + \frac{r_2}{R} \right) \tag{2}$$

where  $T_S$  and D represent the switching period and duty ratio, respectively, and D' is equal to 1 - D.

According to (2), the circuit equation of the output inductor's current in the durations  $0 < t \le DT_S$  and  $DT_S < t \le T_S$  can be obtained at the same time axis, as given in (3), shown at the bottom of the page.

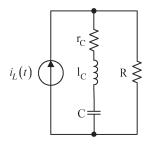

Owing to the output condition of high current and low voltage, a part of the current ripple in the output inductor will flow

into the load. The equivalent circuit for this shunt mechanism is shown in Fig. 3.

According to the equivalent circuit shown in Figs. 2 and 3, the ripple ratio of output voltage  $r_v$  can be derived as

$$r_v \equiv \frac{\Delta E_O}{E_O}$$

$$= \frac{1}{L} \frac{R}{(R+r_C)^2 + \omega^2 l_C^2} \left( \frac{\left[ r_C(R+r_C) + \omega^2 l_C^2 \right] D'}{f_S} + \frac{R l_C}{D} \right)$$

$$\times \left( 1 + \frac{r_{S2} + r_l}{R} \right)$$

(4)

where  $\omega = 2\pi f_S$ .

By using the differential method, the maximum ripple ratio  $r_{v,\max}$  with respect to  $l_C$  can be obtained as (5), where the value of  $l_{C,\max}$ , which causes the  $r_{v,\max}$ , is shown in

$$r_{v,\text{max}} = \frac{R}{L} \left( 1 + \frac{r_2}{R} \right) \left[ \frac{4\pi^2 DD'(R + r_C)g^2 + Rg + DD'R}{Df_S(R + r_C)(1 + 4\pi^2 g^2)} \right]$$

(5)

$$l_{C,\text{max}} = \frac{(R + r_C)}{f_S} \left( DD' + \sqrt{D^2 D'^2 + (1/4\pi^2)} \right)$$

(6)

where

$$g = DD' + \sqrt{D^2D'^2 + (1/4\pi^2)}$$

.

It is shown from (3) that, under the conditions of high switching frequency, low output voltage, and high output current, theoretically, these parasitic elements will definitely affect  $r_v$ . Equations (4) and (5) clearly indicate the existence of the maximum ripple ratio  $r_{v,\mathrm{max}}$  and the specific value of  $l_{C,\mathrm{max}}$  which causes it. They will provide an important reference for choosing the output capacitor in the design phase.

Under the condition of high switching frequency, the ESL of the output capacitor will be affected by many parameters, such as component selecting, printed circuit board layout, circuit wiring, and so on. Therefore, for designing SMPSs with high switching frequency, low output voltage, and high output current, the  $r_{v,\mathrm{max}}$  should be carefully taken into account to ensure  $r_v$  to its specification.

## B. Experimental Results

In order to clarify the shunt mechanism and practical characteristics of  $r_v$ , an experimental prototype is implemented. Tables I and II show the specifications and component values of this prototype, respectively. For observing the output ripple voltage clearly, an external resistor (38.75 m $\Omega$ ) is in series with the output capacitor. Thus, the equivalent  $r_C$  is equal to 42 m $\Omega$ .

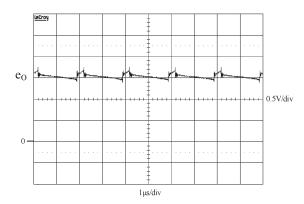

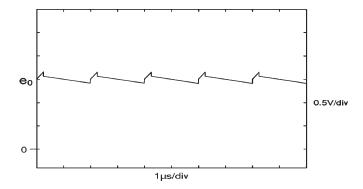

Fig. 6 shows the experimental waveform of the prototype's output voltage. The measured value  $r_v$  in Fig. 4 is 0.158. Under the same condition, the simulated value  $r_v$  according to (4) is 0.146. It is shown that the simulated result is very close to the experimental result.

$$i_{L}(t) = \begin{cases} -\frac{\Delta I_{L}}{2} + \frac{\Delta I_{L}}{DT_{S}} t = \frac{D'E_{O}}{DL} \left( 1 + \frac{r_{2}}{R} \right) \left( t - \frac{DT_{S}}{2} \right), & 0 < t \le DT_{S} \\ \frac{\Delta I_{L}}{2} - \frac{\Delta I_{L}}{D'T_{S}} (t - DT_{S}) = -\frac{E_{O}}{L} \left( 1 + \frac{r_{2}}{R} \right) \left( t - DT_{S} - \frac{D'T_{S}}{2} \right), & DT_{S} < t \le T_{S} \end{cases}$$

(3)

TABLE I SPECIFICATIONS OF THE PROTOTYPE

| Symbol  | Definition          | Value        |

|---------|---------------------|--------------|

| $f_S$   | Switching frequency | 500kHz       |

| Ei      | Input voltage       | 12V          |

| Eo      | Output voltage      | 1.5V         |

| $I_{O}$ | Output current      | 15A          |

| k       | Feedback constant   | $0.17V^{-1}$ |

TABLE II COMPONENT VALUES OF THE PROTOTYPE

| Symbol           | Definition                             | Value                   |

|------------------|----------------------------------------|-------------------------|

| $\mathbf{r}_l$   | Spurious resistance of output inductor | 1.1 mΩ                  |

| $r_{S2}$         | ON resistance of S <sub>2</sub>        | $5.9~\mathrm{m}\Omega$  |

| L                | Output inductance                      | 0.6 μΗ                  |

| С                | Output capacitance                     | 2280 μF                 |

| R                | Load resistance                        | $100~\mathrm{m}\Omega$  |

| $r_{\rm C}$      | ESR of output capacitor                | $3.25~\mathrm{m}\Omega$ |

| $l_{\mathrm{C}}$ | ESL of output capacitor                | 8nH                     |

Fig. 4. Experimental waveform of output voltage  $(r_2=7~{\rm m}\Omega,r_C=42~{\rm m}\Omega,R=100~{\rm m}\Omega,$  and  $l_C=8~{\rm nH}).$

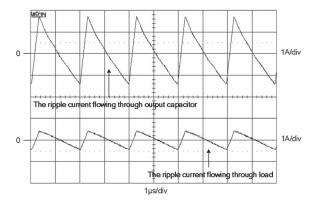

Fig. 5. Output ripple currents.

In this prototype, owing to the ESR of output capacitor that is close to the load resistance under a heavy-load condition, the shunt mechanism of the output ripple current through the load resistance and the output capacitor's ESR can be obviously observed. Fig. 5 shows the practical shunt waveform of output ripple current. It is shown that the ripple current flowing

Fig. 6. Simulated waveform of output voltage  $(r_2=7~{\rm m}\Omega,r_C=42~{\rm m}\Omega,R=100~{\rm m}\Omega,$  and  $l_C=8.6~{\rm nH}).$

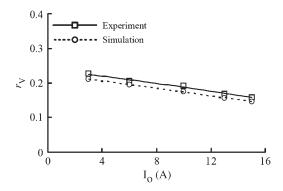

Fig. 7. Simulated and experimental results of  $r_v$  versus  $I_O$ .

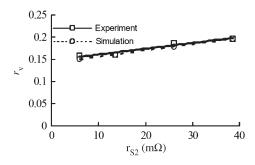

Fig. 8. Simulated and experimental results of  $r_v$  versus  $r_{S2}$ .

through the output capacitor is 2.81 A, and the ripple current flowing through the load is 0.89 A.

For verifying the theoretical analysis, Fig. 6 shows the simulated waveform of the output voltage. Figs. 7–10 show the simulated and experimental  $r_v$ 's with respect to different  $I_O$ ,  $r_{S2}$ ,  $r_C$ , and  $l_C$  values, respectively. All of the simulated results are based on the derived equations shown previously.

From Figs. 4 and 6, it can be seen that the simulated waveform of the output voltage agrees very well with the experimental waveform. Thus, the correctness of the theoretical analysis is confirmed. By varying the load resistance, the experimental results of  $r_v$  versus  $I_O$  can be obtained. Fig. 7 shows both the simulated and experimental results of  $r_v$  versus  $I_O$ . Being different from the  $r_v$  of ideal buck converters,  $r_v$  will vary with  $I_O$  due to parasitic elements. From Fig. 7, it is shown that the experimental results agree well with the simulated results, both of them show that  $r_v$  decreases with the increase of  $I_O$  in this case.

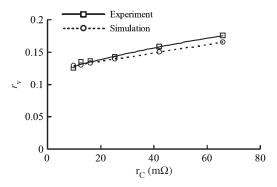

Fig. 9. Simulated and experimental results of  $r_v$  versus  $r_C$ .

Fig. 10. Simulated and experimental results of  $r_v$  versus  $l_C$ .

By adding different resistors in series with  $S_2$ , the experimental results of  $r_v$  versus  $r_{S2}$  can be obtained. Fig. 8 shows both the simulated and experimental results of  $r_v$  versus  $r_{S2}$ . From Fig. 8, the simulated results are almost equal to the experimental results. Both the results show that  $r_v$  increases linearly with the increase of  $r_{S2}$ .

By adding different resistors in series with the output capacitor, the experimental results of  $r_v$  versus  $r_C$  can be obtained. Fig. 9 shows both the simulated and experimental results of  $r_v$  versus  $r_C$ . According to Fig. 9, the simulated results agree well with the experimental results. It is confirmed that  $r_v$  is monotonously increased with the increase of  $r_C$ .

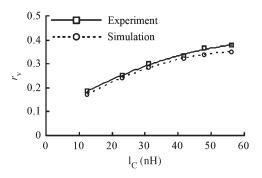

In order to investigate the effects of the output capacitor's ESL on  $r_v$ , different inductors are put in series with the output capacitor. Fig. 10 shows both the simulated and experimental results of  $r_v$  versus  $l_C$ . Based on Fig. 10, it is verified that the simulated results agree well with the experimental results. In this case,  $r_v$  will increase with the increase of  $l_C$ .

From Figs. 7–10, it can be seen that all the experimental results agree well with the simulated results, although there are very small differences between them.

# III. EFFECTS OF THE PARASITIC ELEMENTS ON THE STABILITY

In order to clarify the stability characteristics of the SR buck converter with high output current and low output voltage, this paper investigates the effects of parasitic elements (including the spurious resistance of output inductor  $r_l$ , the ESR of output capacitor  $r_C$ , and the ESL of output capacitor  $l_C$ ) on the stability of such SR buck converter. By using a state-space averaged

Fig. 11. Operation state A.

Fig. 12. Operation state B.

method [29]–[33], the static and dynamic characteristics of the SR buck converter can be obtained.

# A. Analysis of Static and Dynamic Characteristics of the SR Buck Converter

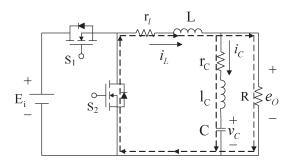

Fig. 1 shows the circuit configuration of the SR buck converter. Based on the circuit operation of the SR buck converter, there are two operation states in one switching period. They are operation states A and B. The operation state A refers to the state that  $S_1$  is ON and  $S_2$  is OFF, and operation state B refers to the state that  $S_1$  is OFF and  $S_2$  is ON. Figs. 11 and 12 show the circuit operations of operation states A and B, respectively. For the simplicity of the stability analysis, the ON resistances of  $S_1$  and  $S_2$  are regarded as the same. Moreover, they are combined in  $r_l$ ; thus, the equivalent  $r_l$  for each operation state is equal to 7.8 m $\Omega$ .

Based on Figs. 11 and 12, the circuit equations of each operation state can be formulated as follows.

For operation state A,

$$L\frac{d}{dt}i_{L} + r_{l}i_{L} + R(i_{L} - i_{C}) = E_{i}$$

$$l_{C}\frac{d}{dt}i_{C} + r_{C}i_{C} + \nu_{C} = R(i_{L} - i_{C})$$

$$C\frac{d}{dt}\nu_{C} - i_{C} = 0.$$

(7)

For operation state B,

$$L\frac{d}{dt}i_{L} + r_{l}i_{L} + R(i_{L} - i_{C}) = 0$$

$$l_{C}\frac{d}{dt}i_{C} + r_{C}i_{C} + \nu_{C} = R(i_{L} - i_{C})$$

$$C\frac{d}{dt}\nu_{C} - i_{C} = 0.$$

(8)

The state-space averaged method is used for the theoretical analysis. From the given equations, the state equations of the SR buck converter can be derived. Thus, the state equations and the static and the dynamic characteristics of the SR buck converter are obtained as follows:

For the state equations,

$$\frac{d}{dt}\hat{\mathbf{X}} = \mathbf{A}\hat{\mathbf{X}} + \mathbf{b}E_i \tag{9}$$

where

$$\mathbf{A} = \begin{bmatrix} -\left(\frac{R+r_l}{L}\right) & \frac{R}{L} & 0\\ \frac{R}{l_C} & -\left(\frac{R+r_C}{l_C}\right) & -\frac{1}{l_C}\\ 0 & \frac{1}{C} & 0 \end{bmatrix}$$

$$\mathbf{b} = \begin{bmatrix} \frac{D}{L}\\ 0\\ 0 \end{bmatrix}$$

$$\hat{\mathbf{X}} = \begin{bmatrix} \hat{i}_L\\ \hat{i}_C\\ \hat{\nu}_C \end{bmatrix}.$$

For the static characteristics (conversion ratio),

$$M \stackrel{\Delta}{=} \frac{E_O}{E_i} = \frac{DR}{r_l + R}.$$

(10)

For the dynamic characteristics,

$$G_{ED}(s) \stackrel{\triangle}{=} \frac{\Delta e_O(s)}{\Delta D(s)}$$

$$= \frac{p_{D0} + p_{D1}s + p_{D2}s^2}{Q_{D0} + Q_{D1}s + Q_{D2}s^2 + Q_{D3}s^3}$$

(11)

where

$$p_{D0} = E_i R$$

$$p_{D1} = E_i R C r_C$$

$$p_{D2} = E_i R C l_C$$

$$Q_{D0} = R + r_l$$

$$Q_{D1} = L + R C (r_l + r_C)$$

$$Q_{D2} = R L C$$

$$Q_{D3} = C L l_C$$

### B. Theoretical and Experimental Results

Based on the prototype's specifications shown in Table I and the derived equations of the static and the dynamic characteristics, the stability characteristics of the SR buck converter can be analyzed in the following two parts.

1) Theoretical Investigation: According to (11), the stability characteristics of the SR buck converter will be affected by many parameters theoretically. Each individual parameter will contribute different influences to the stability characteristics of this converter. Since the load resistance and parasitic elements exist in practical circuits, their combined effects on the stability characteristics will be very complex. In order to analyze the effect of each individual parameter on the stability characteristics, the influence contributed by other parameters shall be minimized.

$\label{eq:table_iii} \text{TABLE III}$  Simulated Phase Margin (  $r_C=0,\,l_C=0,\,\text{and}\,\,r_l=0)$

| I <sub>O</sub> (A) | Phase margin (degree) |

|--------------------|-----------------------|

| 3                  | 2                     |

| 10                 | 5                     |

| 15                 | 8                     |

|                            | Phase margin (degree) |            |             |

|----------------------------|-----------------------|------------|-------------|

| $r_{\rm C} \pmod{m\Omega}$ | $I_O = 3A$            | $I_O = 5A$ | $I_O = 15A$ |

| 3.25                       | 30                    | 34         | 36          |

| 16.2                       | 95                    | 96         | 98          |

| 25.3                       | 108                   | 109        | 110         |

|             | Phase margin (degree) |               |             |

|-------------|-----------------------|---------------|-------------|

| $l_{C}(nH)$ | $I_O = 3A$            | $I_{O} = 10A$ | $I_O = 15A$ |

| 8           | 1.56                  | 5.2           | 7.8         |

| 21.6        | 1.53                  | 5.1           | 7.6         |

| 35          | 1.5                   | 5             | 7.5         |

Thus,  $l_C$ ,  $r_C$ , and  $r_l$  shall be set to zero for investigating the effect of load resistance on the stability of the SR buck converter. According to (11), the phase margin of this converter can be simulated to express the stability characteristics. The simulated results with respect to different output currents are shown in Table III. As shown in Table III, when  $l_C$ ,  $r_C$ , and  $r_l$  are all equal to zero, theoretically, the phase margin is slightly increased.

For investigating the effects of the output capacitor's ESR  $(r_C)$  on the stability of the SR buck converter,  $l_C$  and  $r_l$  shall be set to zero. The simulated results with respect to different  $r_C$ 's and different output currents are shown in Table IV.

From Table IV, when  $l_C$  and  $r_l$  are equal to zero, theoretically, the phase margin will increase with the increase of  $r_C$  and output current.

For investigating the effects of the ESL of output capacitor  $(l_C)$  on the stability of the SR buck converter,  $r_l$  and  $r_C$  shall be set to zero. The simulated results with respect to different  $L_l$ 's and different output currents are shown in Table V.

As can be observed in Table V, when  $r_l$  and  $r_C$  are equal to zero, theoretically, the phase margin will slightly increase with the increase of output current. Moreover, the increase of  $l_C$  has no effect on the phase margin.

2) Comparison of the Theoretical and Experimental Results: To investigate the practical stability characteristics of the SR buck converter, the gain and phase measurements are needed to verify the simulated Bode diagrams. With the comparison of the theoretical and experimental results, the theoretical and practical performances on the stability of this prototype will be clarified. For the most severe condition of the stability, the output current is fixed at a light load  $(I_O=3~{\rm A})$  in the experiments.

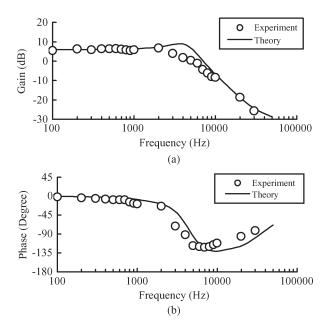

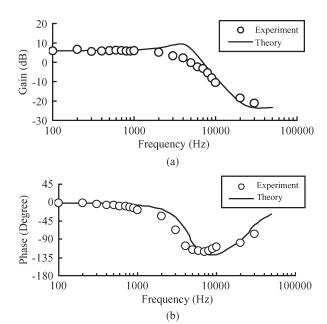

To investigate the effects of the output capacitor's ESR  $(r_C)$  on the stability of the prototype, the parameters except  $r_C$  are fixed in the experiments. The experimental and theoretical

Fig. 13. Bode diagram of the prototype ( $I_O=3~{\rm A}, r_l=7.8~{\rm m}\Omega,$   $l_C=8~{\rm nH},$  and  $r_C=3.25~{\rm m}\Omega).$  (a) Gain. (b) Phase.

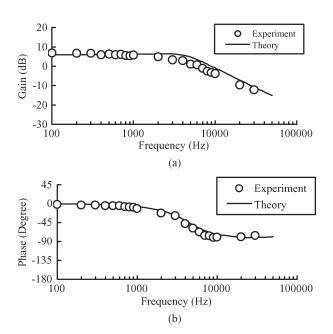

Fig. 14. Bode diagram of the prototype ( $I_O=3~{\rm A}, r_l=7.8~{\rm m}\Omega,$   $l_C=8~{\rm nH},$  and  $r_C=16.2~{\rm m}\Omega).$  (a) Gain. (b) Phase.

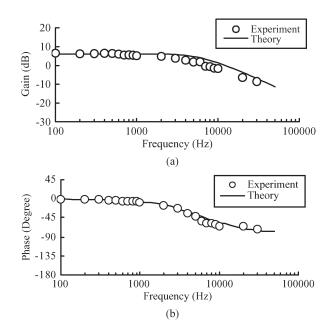

results with different  $r_C$ 's under a light load ( $I_O=3~{\rm A}$ ) are shown in Figs. 13–15, respectively.

As can be observed from Figs. 13–15, the experimental results agree well with the theoretical results. For the convenient of analysis, all the simulated and experimental phase margins are listed in Table VI. According to Table VI, as  $r_l$  and  $l_C$  are fixed under the condition of light load, theoretically and experimentally, the phase margin will obviously increase with the increase of  $r_C$ .

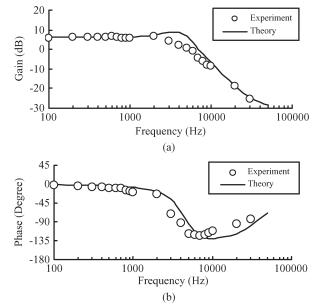

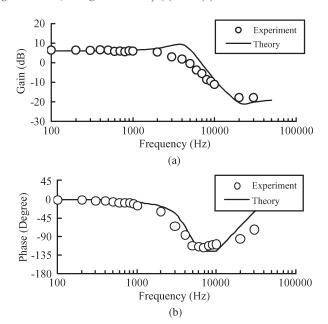

To investigate the effects of the ESL of output capacitor  $(l_C)$  on the stability of the prototype, the parameters except  $l_C$  are fixed in the experiments. The experimental and theoretical

Fig. 15. Bode diagram of the prototype  $(I_O=3~{\rm A}, r_l=7.8~{\rm m}\Omega,~l_C=8~{\rm nH},$  and  $r_C=25.3~{\rm m}\Omega).$

TABLE VI EXPERIMENTAL AND SIMULATED PHASE MARGINS ( $I_O=3~{\rm A},$   $r_l=7.8~{\rm m}\Omega,$  and  $l_C=8~{\rm nH})$

|                      | Theory       | Experiment   |

|----------------------|--------------|--------------|

| $r_{\rm C}(m\Omega)$ | Phase margin | Phase margin |

| 1C (11175)           | (degree)     | (degree)     |

| 3.25                 | 53           | 62           |

| 16.2                 | 108          | 112          |

| 25.3                 | 118          | 121          |

Fig. 16. Bode diagram of the prototype ( $I_O=3~{\rm A}, r_l=7.8~{\rm m}\Omega,$   $l_C=8~{\rm nH},$  and  $r_C=3.25~{\rm m}\Omega).$  (a) Gain. (b) Phase.

results under a light load ( $I_O=3~{\rm A}, r_C=3.25~{\rm m}\Omega$ , and  $r_l=7.8~{\rm m}\Omega$ ) are shown in Figs. 16–18, respectively.

As can be observed from Figs. 16-18, the experimental results agree well with the theoretical results. According to

Fig. 17. Bode diagram of the prototype ( $I_O=3~{\rm A}, r_l=7.8~{\rm m}\Omega,$   $l_C=21.6~{\rm nH},$  and  $r_C=3.25~{\rm m}\Omega).$  (a) Gain. (b) Phase.

Fig. 18. Bode diagram of the prototype ( $I_O=3~$  A,  $r_l=7.8~$  m $\Omega$ ,  $l_C=35$  nH, and  $r_C=3.25$  m $\Omega$ ). (a) Gain. (b) Phase.

TABLE VII EXPERIMENTAL AND SIMULATED PHASE MARGINS (  $I_O=3~{\rm A}, r_l=7.8~{\rm m}\Omega,$  and  $r_C=3.25~{\rm m}\Omega)$

|             | Theory       | Experiment   |

|-------------|--------------|--------------|

| 1 (nH)      | Phase margin | Phase margin |

| $l_{C}(nH)$ | (degree)     | (degree)     |

| 8           | 53           | 62           |

| 21.6        | 55           | 64           |

| 35          | 57           | 67           |

Figs. 16–18, the simulated and experimental phase margins are listed in Table VII. From Table VII, as  $r_l$  and  $r_C$  are fixed under the condition of a light load, the phase margin will slightly increase with the increase of  $l_C$  by both theory and experiment.

#### IV. DISCUSSION

Since the effects of parasitic elements on converters are fairly complex and able to be ignored for some cases, these elements are not usually taken into account at the design phase. However, under the conditions of high switching frequency, low output voltage, and high output current, the effects of the parasitic elements on circuit operation should be paid with attention.

Based on previous two sections, it is clear that the parasitic elements will affect the output ripple voltage and the stability of the whole circuit.

For the output ripple voltage, the following design considerations are summarized.

- 1)  $r_v$  will increase linearly with the increase of  $r_{S2}$ .

- 2)  $r_v$  is monotonously increased with the increase of  $r_C$ .

- 3)  $r_v$  will increase with the increase of  $l_C$ .

- 4) Equations (5) and (6) clearly indicate the existence of the maximum ripple ratio  $r_{v,\max}$  and the specific value of  $l_{C,\max}$  which causes it. This point of view will provide an important reference for choosing the output capacitor in the design phase.

For the stability, the following design considerations are summarized.

- 1) As  $r_l$ ,  $r_C$ , and  $l_C$  are zero, theoretically, the stability of the circuit will slightly increase with the increase of the load current.

- 2) As  $r_l$  and  $l_C$  are fixed, theoretically and experimentally, the phase margin will obviously increase with the increase of  $r_C$ .

- 3) As  $r_l$  and  $r_C$  are fixed, theoretically and experimentally, the phase margin will slightly increase with the increase of  $l_C$ .

Normally, it is believed that  $l_C$  will be adverse to the stability. However, it is found from this research that not only  $r_C$  but also  $l_C$  can improve the stability of the SR buck converter.

On the other hand, the output ripple voltage will increase with the increase of  $r_C$  and  $l_C$ . Therefore, for a balanced design on the ripple voltage and the stability, choosing an output capacitor with reasonable  $r_C$  and  $l_C$  will be helpful. Within the reasonable range of  $r_C$  and  $l_C$ , the output capacitor with larger  $l_C$  and smaller  $r_C$  is acceptable for higher output efficiency. A design example is shown as follows.

Generally, the reasonable value of  $r_C$  is about several milliohms to tens of milliohms (in this paper, 5–25 m $\Omega$ ), and the reasonable value of  $l_C$  is about several nanohenrys to tens of nanohenrys (in this paper, 5–25 nH). Under the condition of  $E_i=12$  V,  $E_O=1.5$  V,  $I_O=3$  A,  $f_S=500$  kHz,  $r_l=1.1$  m $\Omega$ ,  $r_{S2}=5.9$  m $\Omega$ , L=0.6  $\mu$ H, and C=2280  $\mu$ F, the simulated results of phase margin with respect to different  $r_C$ 's and different  $l_C$ 's are shown in Table VIII. According to Table VIII, the value of  $r_C$  should be chosen between 15 and 25 m $\Omega$  for obtaining enough phase margin (greater than  $100^\circ$ ).

Since the value of  $r_C$  is decided between 15 and 25 m $\Omega$ , the simulated results of  $r_v$  versus  $l_C$  can be seen in Fig. 19. According to Fig. 19, it is shown in this figure that the ripple ratio of the output voltage  $r_v$  with respect to two kinds of  $r_C$  is almost the same (the maximum difference between two curves

|                        | Ü                     |                      | Ü                    |

|------------------------|-----------------------|----------------------|----------------------|

|                        | Phase margin (degree) |                      |                      |

| $r_{C} \pmod{m\Omega}$ | l <sub>C</sub> =5nH   | 1 <sub>C</sub> =15nH | l <sub>C</sub> =25nH |

| 5                      | 65                    | 67                   | 68                   |

| 10                     | 91                    | 93                   | 94                   |

| 15                     | 105                   | 107                  | 109                  |

| 20                     | 113                   | 115                  | 117                  |

| 25                     | 117                   | 119                  | 121                  |

| 0.35 |                   | - ABB            |   |

|------|-------------------|------------------|---|

| 0.25 |                   |                  |   |

| 0.2  |                   |                  |   |

| 0.15 |                   |                  |   |

| 0.1  |                   | <b>o</b> rc=15mΩ | 7 |

| 0.05 |                   | <b>□</b> rc=25mΩ | ╛ |

| 00   | 10                | 20               |   |

|      | l <sub>C</sub> (1 |                  |   |

Fig. 19. Simulated results of  $r_v$  versus  $l_C$  (taking  $r_C$  as a parameter).

is 0.014). Based on the aforementioned results, an  $l_C$  of 25 nH and an  $r_C$  of 15 m $\Omega$  can be used to obtain enough phase margin and reduce the power dissipation of  $r_C$ .

#### V. CONCLUSION

For SR buck converters with high output current and low output voltage, the parasitic elements have affected the circuit characteristics remarkably, particularly the output ripple voltage and stability. Moreover, in this paper, it has been shown that these parasitic elements link the ripple ratio of the output voltage and the stability.

All the research findings will provide designers an important reference to estimate the effects of the parasitic elements. With these design considerations, designers can make a good tradeoff on the circuit design and the component selection in the design phase.

#### REFERENCES

- [1] D. Garinto, "A new converter architecture for future generations of microprocessors," in *Proc. IEEE IPEMC*, 2006, vol. 1, pp. 1–6.

- [2] A. Simon-Muela, S. Petibon, C. Alonso, and J. L. Chaptal, "Practical implementation of a high-frequency current-sense technique for VRM," *IEEE Trans. Ind. Electron.*, vol. 55, no. 9, pp. 3221–3230, Sep. 2008.

- [3] M. Castilla, L. G. de Vicuna, J. M. Guerrero, J. Matas, and J. Miret, "Designing VRM hysteretic controllers for optimal transient response," *IEEE Trans. Ind. Electron.*, vol. 54, no. 3, pp. 1726–1738, Jun. 2007.

- [4] P.-L. Wong, F. C. Lee, X. Zhou, and J. Chen, "VRM transient study and output filter design for future processors," in *Proc. IEEE IECON*, 1998, pp. 410–415.

- [5] M. T. Zhang, M. M. Jovanovic, and F. C. Lee, "Design considerations for low-voltage on-board DC/DC modules for next generations of data processing circuits," *IEEE Trans. Power Electron.*, vol. 11, no. 2, pp. 328–337, Mar. 1996.

- [6] J.-J. Lee and B.-H. Kwon, "DC–DC converter using a multiple-coupled inductor for low output voltages," *IEEE Trans. Ind. Electron.*, vol. 54, no. 1, pp. 467–478, Feb. 2007.

- [7] S.-S. Lee, S.-W. Choi, and G.-W. Moon, "High-efficiency active-clamp forward converter with transient current build-up (TCB) ZVS technique," *IEEE Trans. Ind. Electron.*, vol. 54, no. 1, pp. 310–318, Feb. 2007.

- [8] J.-J. Lee, J.-M. Kwon, E.-H. Kim, W.-Y. Choi, and B.-H. Kwon, "Single-stage single-switch PFC flyback converter using a synchronous rectifier," *IEEE Trans. Ind. Electron.*, vol. 55, no. 3, pp. 1352–1365, Mar. 2008.

- [9] P.-Y. Chen, M. Jinno, and Y.-M. Shie, "Research on the reverse conduction of synchronous rectifiers," *IEEE Trans. Ind. Electron.*, vol. 55, no. 4, pp. 1570–1575, Apr. 2008.

- [10] H.-J. Chiu and L.-W. Lin, "A high-efficiency soft-switched AC/DC converter with current-doubler synchronous rectification," *IEEE Trans. Ind. Electron.*, vol. 52, no. 3, pp. 709–718, Jun. 2005.

- [11] D. Fu, B. Lu, and F. C. Lee, "1 MHz high efficiency LLC resonant converters with synchronous rectifier," in *Proc. IEEE PESC*, 2007, pp. 2404–2410.

- [12] G.-C. Hsieh, C.-Y. Tsai, and W.-L. Hsu, "Synchronous rectification LLC series-resonant converter," in *Proc. IEEE APEC*, 2007, pp. 1003–1009.

- [13] M. Jinno, P.-Y. Chen, and Y.-M. Shie, "Study on the reverse conduction of synchronous rectifiers," in *Proc. IEEE TENCON*, 2006, pp. 1–4.

- [14] T. Qian, W. Song, and B. Lehman, "Self-driven synchronous rectification scheme for wide range application of DC/DC converters with symmetrically driven transformers," in *Proc. IEEE PESC*, 2006, pp. 1–6.

- [15] T. Senanayake and T. Ninomiya, "Autoreset forward DC–DC converter with self-driven synchronous rectification," in *Proc. IEEE PESC*, 2004, vol. 5, pp. 3636–3641.

- [16] H. Visairo, E. Rodriguez, J. A. Cobos, and P. Alou, "Multiphase voltage regulator module with self-driven synchronous rectification," in *Proc. IEEE PESC*, 2003, vol. 1, pp. 132–137.

- [17] A. Fernandez, J. Sebastian, M. M. Hernando, P. Villegas, and J. Garcia, "New self-driven synchronous rectification system for converters with a symmetrically driven transformer," in *Proc. IEEE APEC*, 2003, vol. 1, pp. 352–358.

- [18] K. Murata and K. Harada, "Analysis of a self turn-on phenomenon on the synchronous rectifier in a DC–DC converter," in *Proc. IEEE INTELEC*, 2003, pp. 199–204.

- [19] K. Kuwabara, H. Matsuo, K. Kobayashi, and K. Nishimura, "A novel synchronous rectification circuit using a saturable current transformer," in *Proc. IEEE PESC*, 2002, vol. 1, pp. 143–148.

- [20] M. Jinno, "Efficiency improvement for SR forward converters with LC snubber," IEEE Trans. Power Electron., vol. 16, no. 6, pp. 812–820, Nov. 2001.

- [21] T. Kohama, T. Ninomiya, M. Shoyama, and R. Tymerski, "Analysis of abnormal phenomena caused by synchronous rectifiers in a paralleled converter system," *IEEE Trans. Power Electron.*, vol. 15, no. 4, pp. 670– 680, Jul. 2000.

- [22] X. Zhou, M. Donati, L. Amoroso, and F. C. Lee, "Improve light load efficiency for synchronous rectifier buck converter," in *Proc. IEEE APEC*, 1999, vol. 1, pp. 295–305.

- [23] O. Djekic, M. Brkovic, and A. Roy, "High frequency synchronous buck converter for low voltage applications," in *Proc. IEEE PESC*, 1998, vol. 2, pp. 1248–1254.

- [24] R. T. Chen, "Single-stage autotransformer-based VRM with input current shaper," *IEEE Trans. Power Electron.*, vol. 22, no. 6, pp. 2375–2385, Nov. 2007.

- [25] D. Garinto, "A novel multiphase multi-interleaving buck converters for future microprocessors," in *Proc. IEEE IPEMC*, 2006, pp. 82–87.

- [26] J. Sun, "Characterization and performance comparison of ripple-based control for voltage regulator modules," *IEEE Trans. Power Electron.*, vol. 21, no. 2, pp. 346–353, Mar. 2006.

- [27] X. Cao and R. Oruganti, "Fast response control of stepping inductance voltage regulator module," in *Proc. IEEE PESC*, 2005, pp. 382–388.

- [28] A. M. Wu and S. R. Sanders, "An active clamp circuit for voltage regulation module (VRM) applications," *IEEE Trans. Power Electron.*, vol. 16, no. 5, pp. 623–634, Sep. 2001.

- [29] R. P. Burgos, E. P. Wiechmann, and J. Holtz, "Complex state-space modeling and nonlinear control of active front-end converters," *IEEE Trans. Ind. Electron.*, vol. 52, no. 2, pp. 363–377, Apr. 2005.

- [30] A. Emadi, "Modeling and analysis of multiconverter DC power electronic systems using the generalized state-space averaging method," *IEEE Trans. Ind. Electron.*, vol. 51, no. 3, pp. 661–668, Jun. 2004.

- [31] J. Sun, D. M. Mitchell, M. F. Greuel, P. T. Krein, and R. M. Bass, "Averaged modeling of PWM converters operating in discontinuous conduction mode," *IEEE Trans. Power Electron.*, vol. 16, no. 4, pp. 482–492, Jul. 2001.

- [32] T. Ninomiya, M. Nakahara, T. Higashi, and K. Harada, "A unified analysis of resonant converters," *IEEE Trans. Power Electron.*, vol. 6, no. 2, pp. 260–270, Apr. 1991.

- [33] R. D. Middlebrook, "Small-signal modeling of pulse-width modulated switched-mode power converters," *Proc. IEEE*, vol. 76, no. 4, pp. 343–354, Apr. 1988.

Masahito Jinno received the B.S. degree in electrical engineering from National Cheng Kung University, Tainan City, Taiwan, in 1975, and the M.S. and Dr.Eng. degrees in electronics from Kyushu University, Fukuoka, Japan, in 1982 and 1985, respectively.

He has been involved in research and development of switched-mode power supplies, uninterruptible power systems, and inverters for over 20 years. Since 2002, he has been a Professor in the Department of Electrical Engineering, I-Shou University, Dashu Township, Taiwan. His current

research interest includes power electronics, particularly electromagnetic interference and reliability.

**Po-Yuan Chen** received the B.E. and M.E. degrees in electrical engineering from I-Shou University, Dashu Township, Taiwan, in 1999 and 2002, respectively, where he is currently working toward the Ph.D. degree in the Department of Electrical Engineering.

His research interests include the field of power electronics.

**Yu-Chun Lai** received the B.E. and M.E. degrees in electrical engineering from I-Shou University, Dashu Township, Taiwan, in 2005 and 2008, respectively.

He is currently with the Department of Electrical Engineering, I-Shou University. His research interests include the field of power electronics.

**Koosuke Harada** (F'80) was born in Japan on November 10, 1929. He received the B.S. degree in electrical engineering and the Dr.Eng. degree from Kyushu University, Fukuoka, Japan, in 1953 and 1958, respectively.

From 1968 to 1993, he was a Professor at Kyushu University. Since 1993, he has been a Professor and the Director of the Energy Electronics Laboratory, Sojo University (formerly Kumamoto Institute of Technology), Kumamoto, Japan. He is currently a Professor Emeritus at Kyushu University.

Dr. Harada received the IEEE William E. Newell Power Electronics Award in 1988 and the IEEE Magnetics Society Achievement Award in 1996. He served as General Chairman of the 1988 IEEE Power Electronics Specialists Conference and the 1992 International Telecommunications Energy Conference.