دانلود شبیه سازی آزمایشات مدار منطقی و سیستم های دیجیتال با پروتئوس

این پروژه شامل انجام هشت آزمایش در زمینه پیاده سازی مدار منطقی و سیستم های دیجیتال در محیط نرم افزار پروتئوس می باشد: این آزمایشات شامل موارد زیر می باشند: 1. شبیه سازی مدار آی سی 7408 2. مدار full adder 3. مدار جمع کننده 4 بیتی 4. مدار تشخیص سرریز 5. جمع کننده 8 بیتی با اتصال دو جمع کننده 4 بیتی 6. مدار جمع کننده تفریق کننده 7. مدار مقایسه کننده 8. مدار تولید کننده بیت توازن زوج

| گزارشکار: دارد (44 صفحه در قالب فایل pdf) | شبیه سازی : دارد (پروتئوس و در فرمت های .pdsprj. & pdsbak) (هشت پوشه جداگانه شامل فایل های شبیه سازی برای هشت آزمایش که صورت مساله آنها مشخص شده است) |

پیاده سازی مدار منطقی در محیط پروتئوس

در ابتدا به توضیحاتی در مورد مدار منطقی می پردازیم:

گیت منطقی، یک مدل ایده آل از پیاده سازی دستگاه های الکترونیکی فیزیکی یا محاسباتی ، بر اساس تابع بولی است. یک عمل منطقی روی یک یا تعداد بیشتری از ورودی های باینری صورت می گیرد که یک خروجی باینری تکی را تولید می کند. با توجه به موقعیت زمینه ای ، این مفهوم اشاره به گیت منطقی ایده آل دارد. برای مثال این گیت دارای زمان بالارفتن 0 و پهنای خروجی (FAN OUT) نامحدود است. یا ممکن است برای اشاره به دستگاه فیزیکی غیرایده آل بکار برود. گیت های منطقی ، در ابتدا بر اساس دیودها یا ترانزیستورهای فعال روی سوئیچ های برقی عمل می کنند. البته امکان ساخت آن ها بر اساس لوله های خلا، رله های الکترومغناطیسی (منطقه رله) ، منطق سیالاتی، منطق پنوماتیک، نوری ، مولکول ها، یا حتی مولفه های مکانیکی نیز وجود دارد. در تقویت ، گیت های منطقی به صورت آبشاری بگونه ای مستقر شده که توابع بولی ایجاد بشوند. لذا امکان ساخت مدل فیزیکی از تمامی منطق های بولی فراهم می شود. همچنین می توان تمامی الگوریتم ها و عملیات ریاضیاتی توصیف پذیر بر اساس منطق بولی را اجرا نمود. مدارات منطقی ، دارای دستگاه هایی همچون مولتی پلکسرها، ثبات ها، واحدهای منطق حسابی (ALU)، و حافظه رایانه ای هستند و تا میکروپردازنده کامل ادامه می یابند. آن ها ممکن است شامل 100 میلیون گیت باشند. در روش های مدرن، اکثر گیت ها از ماسفت (ترانزیستور اثر میدان با نیمه هادی متال اکسید ) ساخته شده اند. گیت های منطقی ترکیبی AND-OR – معکوس (AOI) یا OR-AND- معکوس (OAI) ، معمولاً در طراحی مدارات بکار می روند زیرا ساخت شان بر اساس ماسفت ساده تر، و بهینه تر از مجموع گیت های تکی است. در منطق معکوس پذیر، از گیت های تافلی استفاده می شود.

در ادامه به توضیحات مربوط به این پروژه می پردازیم همانطور که در قسمت خلاصه ذکر شد، این پروژه شامل 8 آزمایش می باشد؛ در ادامه به بررسی آزمایش اول و پنجم پرداخته ایم:

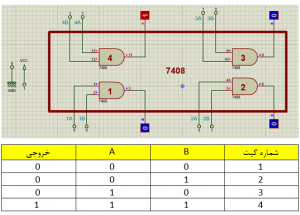

مدار آی سی 7408 در محیط نرم افزار پروتئوس ترسیم شده است که شامل 4 گیت AND می باشد. به هر کدام از این گیت ها، ورودی هایی به صورت پورت متصل شده و خروجی ها نیز از طریق logic probe قابل مشاهده و بررسی هستند.

همانطور که مشاهده می گردد، در حالت A=1 و B=1، خروجی برابر 1 بوده و در حالات دیگر نیز برابر صفر است. توضیحات تکمیلی این آزمایش در فایل گزارشکار داخل محصول، قرار داده شده است.

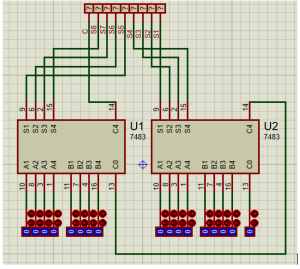

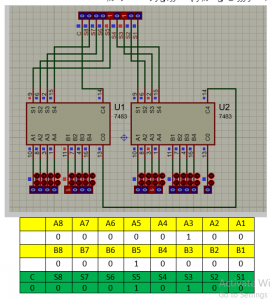

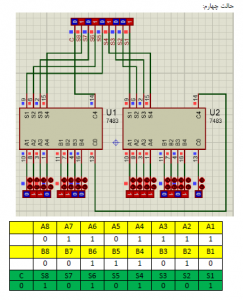

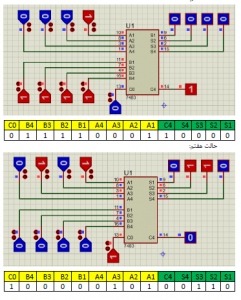

مطابق فرضیات این آزمایش، دو جمع کننده 7483 را کنار هم قرار میدهیم. C0 اولی را برابر صفر قرار داده و C0 دومی را به C4 وصل می کنیم.

به مدار، ورودی می دهیم و خروجی ها را یادداشت می کنیم

توضیحات تکمیلی این آزمایش نیز داخل گزارشکار جامع، آورده شده است.

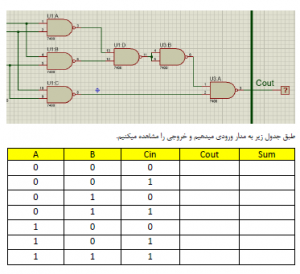

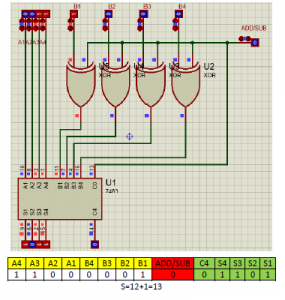

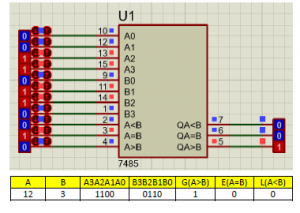

در ادامه نیز تعدادی از تصاویر مربوط به این شبیه سازی قرار داده شده است:

دیدگاهها

هیچ دیدگاهی برای این محصول نوشته نشده است.